新晶体管制造工艺技术前瞻

2.解决方案二:转向全耗尽型

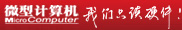

ETSOI(FD-ETSOI)技术正如我们上文所介绍的那样,虽然立体型晶体管结构具有很多优点,但其制造工艺的复杂性则会令不少厂商望而却步,如果能继续延续平面型工艺的寿命,那么无论在风险还是成本方面的担忧都会大大减小。这便是IBM公司推出全耗尽型超薄SOI(FDETSOI)的目的所在。IBM 公司2009年12月份曾经展示了一种基于ETSOI(Extremely Thin SOI:超薄SOI)的22nm制程FD-ETSOI工艺,并在IEDM2009会议上展示了22nm FDETSOI晶体管制造流程图(图11):

图11

IBM专家表示:“我们采用的是不会损害ETSOI层的就地掺杂技术(in-situ doping)。我们首先生成栅极隔离层;然后在漏源区用外延技术沉积生长出漏/源极,形成外延层并在漏/源极的生长过程中同时就地掺杂所需的杂质元素;此后我们会对晶体管进行加热处理,令漏源极中的掺杂原子向沟道方向扩散,形成扩散层(图11中的ext)。而加热处理过程中我们使用的尖峰退火技术(Spike Anneal)则不会对ETSOI层的结构造成不必要的损害。”那么这个如此强大的FD-ETSOI工艺,其晶体管结构是怎样的呢?

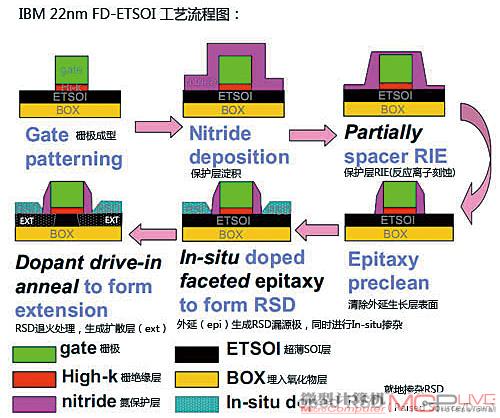

图12

如图12可见,这种22nm FDETSOI工艺的本质是将位于埋入式氧化物(BOX)上方的SOI层的厚度缩小到极低的水平,使用这种技术之后,22nm制程中的SOI层的厚度仅有6.3nm,而传统的SOI层厚度通常在 20nm以上,发展到15nm制程,SOI层的厚度还可以进一步被缩小到5nm左右。极薄的SOI层厚度保证了全耗尽设计的实现。当然,如此薄厚度的SOI层制作起来并非易事,要想将整片晶圆上的SOI层厚度控制在一定的误差水平之内,其制作难度可想而知。据IBM表示,目前由Soitec公司提供,能用于制造ETSOI产品的SOI晶圆数量仍十分有限,不过他们已经可以把这种SOI层的厚度误差控制在±5埃左右。除了对晶圆厂商提出了较高的要求之外,FD-ETSOI技术还存在其它的难点,由于SOI层的厚度极薄,因此很容易受到损坏。而且为了避免对SOI层造成损坏,在制造漏/源极时不能采用传统破坏性较强的离子注入技术,必须采用就地掺杂技术(In-situ Doping)。

隶属IBM技术同盟的GobalFoundries的技术开发经理John Pellerin表示,FD-SOI技术从应用结构上看与现有的PD-SOI技术非常相近,“我们只需要把SOI层的厚度变薄,并想办法解决ETSOI带来的一些问题即可,其它的部分则和传统的制造工艺基本相同。”当然ETSOI技术仍有许多其他的问题需要解决,比如如何减小器件的寄生电阻等。

尽管凭借FD-ETSOI技术仍可暂时延长平面型晶体管工艺的寿命,但要真正将这种技术投入实用同样需要解决很多难题,故FD-ETSOI技术仍可算得上是对传统制造技术的一次较大变革。

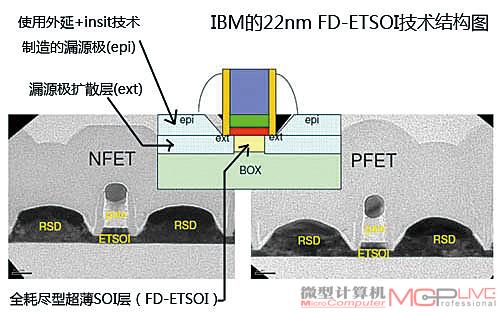

2.继续ETSOI的辅助技术:SiC应变硅技术

说到IBM的22nm FD-ETSOI技术,便不能不提其中采用的一种辅助型应变硅技术SiC。与我们前面提到的eSiGe类似,这也是一种应变硅技术,所不同的是eSiGe面向的对象是PMOS管中的沟道,而SiC则面向NMOS管中的沟道。

与eSiGe能为PMOS管沟道的纵向方向施加应变力的道理相反,由于C原子的体积比Si原子小,因此SiC化合物的晶格常数比Si小,这样当把SiC层嵌入NMOS管的漏源极之后,便可对沟道纵向方向施加拉伸应变力,如图13所示:

图13

IBM在描述自己的FD-ETSOI工艺时曾经提到,他们会在沉积NMOS管的漏源极时向极内掺杂碳杂质。而且另外一家IBM工艺技术联盟的成员Applied Mater ials公司也分别在IEDM2008和2009年的Semicon会展上两次强调了这种SiC应变硅技术的可行性。那么外界对SiC技术的评价如何呢?

有趣的是,Intel过去也曾经对SiC技术进行了深入的研究,不过他们现在似乎完全改变了对待SiC应变硅技术的态度,Intel过去曾经表示他们将有望使用SiC应变硅技术,不过近Intel公司的有关人员在IEDM2009会议中接受采访时则表示不愿意就Intel在SiC应变硅技术方面取得的进展发表任何评论。而会上代表Intel做有关Intel 32nm制程技术演讲的Paul Packan则在演讲后回答记者提问的环节干脆没有理会一位记者提出的有关SiC应变硅技术在32nm制程NMOS结构中应用状况的问题。

GlobalFoundries公司的Pellerin表示:“我们正在关注SiC应变硅技术,并且正在考虑在我们的22nm制程及更高级别制程中使用这项技术。”在目前的工艺尺寸条件情况下,要想很好地控制漏源区的离子注入过程将是一项非常复杂的任务,而在IBM的FD-ETSOI工艺中,NMOS中使用的SiC应变硅技术则与PMOS中的SiGe应变硅技术一样是采用外延沉积实现的,不必再为如何控制离子注入而担忧。同时这位专家也表示:“如何在NMOS管中应用应变硅技术将是另外一个改善晶体管性能的关键技术。”

3.解决方案三:转向III-V族技术

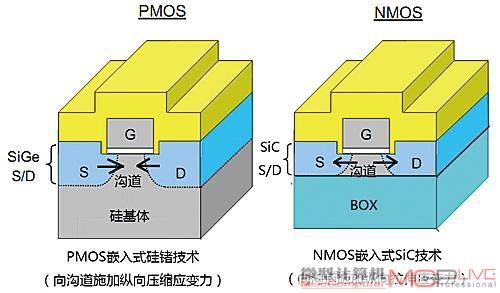

III-V族技术是另外一种很有希望的晶体管技术发展方向,这种方案的特点是采用位于元素周期表中III-V族元素组成的材料来替代现有MOSFET管的材料,因此人们便将这种技术形象地称为“III-V族”技术,也有将采用这种技术制作的场效应管称为“QWFET”的。图14是Intel在IDEM2009会展上展示的他们在使用这种技术制造的QWFET场效应管方面取得的新进展,当时他们向这种晶体管结构中引入了High-K栅极氧化物层,这种新的High-K栅氧化物层的加入,大大减小了QWFET的漏电现象。

图14

从图14中可见,III-V族技术同样也可以在保证传统平面型晶体管制造工艺变化不大的基础上制造出关键尺寸符合发展要求的产品。

在IEDM2009会议上,来自斯坦福大学的教授Krishna Saraswat还表示,当沟道宽度降至10nm左右时,必须采用新材料来制造沟道。据他估计,业界将首先开发出NMOS管使用III-V族元素构建沟道,PMOS管使用锗元素构建沟道的技术,然后再向PMOS/NMOS统一采用III- V族元素制造沟道的方向发展。转向使用III-V族元素将大大减小器件的工作电压和管子的能耗,可将管子的工作电压减小至仅0.5V。

总结

回归到大家关心的新制程技术在Intel/AMD产品的实际应用方面,笔者认为Intel和AMD会继续走自己的老路。其中Intel不太可能会使用ET SOI技术, IBM/GlobalFoundries/AMD则会继续将SOI发扬光大。其理由很简单,因为Intel如果采用三门晶体管技术,便可以绕开SOI。与Intel会尽可能地延长体硅制程寿命的作法截然相反的是,IBM/GlobalFoundries/AMD则会尽快转向FD-ETSOI技术,并尽全力延续FD-ETSOI的寿命。但从技术角度来分析,两者又是在统一中追求变化,都在向全耗尽型立体晶体管转变。当然,新技术的推出有时是无法按常理推测的,到底哪个方向是正确的我们还不得而知。这就好比现在我们在不停地寻找方法或者更换交通工具,也许哪一天会去改造路面的材料甚至结构,甚至于将来的某一天去调整前进路上的空气阻力,或者突然有人告诉我们:“现在可以不走这条路了,我们发现了另一条路”,也许在陆地上,也许存在于水中、空中!在制程工艺不断发展之路上,“Intel”和“AMD”们也在不停地更换“工具”,以便让自己前进得更快、更舒服一些。