新晶体管制造工艺技术前瞻

延续现有晶体管架构

应变硅与HKMG——延续传统平面型晶体管的希望

在过去的几十年中,为了延续传统平面型晶体管制造技术的寿命,弥补关键尺寸缩小给传统平面型晶体管带来的负面效应,以Intel、台积电、AMD(也就是现在的GlobalFoundries)为代表的制造厂商已经开发出了很多能够改善传统平面型晶体管性能的技术,这些技术中,已经投入商用的技术尤以面向改善沟道性能的应变硅技术和改善栅极性能的HKMG(High-K栅氧化物层+金属栅极,此后简称HKMG)技术为代表,自从Intel在90nm制程的Pentium 4处理器上首次启用应变硅技术之后,这两种主要的辅助技术便成了各家厂商开发制程技术的两大热点,各家厂商均先后在自家制程工艺中加入了类似的技术,Intel和AMD包括台积电都在90~32nm的演进过程中采用了应变硅技术和HKMG技术,尽管他们的具体实现手法不同。为了读者能够更好的理解本文,下面我们就对这两种技术进行简单的介绍。

a.应变硅技术

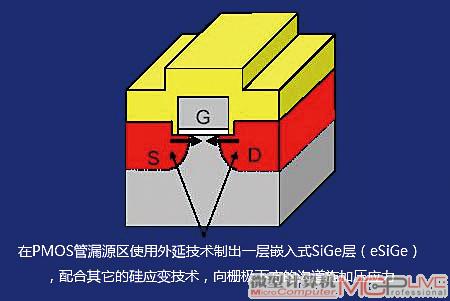

注意图3中的“启用eSiGe(嵌入式硅锗)材料”,指的便是专门用于改善传统平面型晶体管管沟道性能的应变硅技术中的一种,应变硅技术的实质是改善沟道中空穴/电子流动的速度。

图3

eSiGe技术主要面向PMOS管,其原理是在PMOS管的漏源区外延生长一层晶格常数(即晶格原子之间的距离)比PMOS沟道中硅材料的晶格常数更大的SiGe层,以此来生成对PMOS管沟道压缩应力的技术,其原理如图3所示。根据研究,当向PMOS管沟道施加纵向(即栅极宽度方向)的压缩应力时,可以大大改善沟道的载流子移动性,提升效率。

PMOS是指N型衬底、P沟道,靠空穴的流动运送电流的MOS管,全称为P-channel Metal Oxide Semiconductor FET;NMOS是指P型衬底,N沟道,依靠电子的流动来运行电流的MOS管。全称为N-channel Metal Oxide Semiconductor FET。

b.HKMG技术

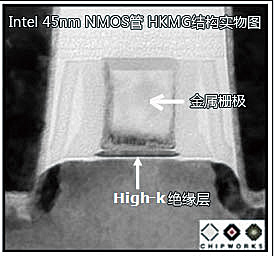

HKMG是以High-K绝缘层替代传统的SiO2氧化层,并以金属材料栅极替换旧有的硅材料栅极的一项技术,这项技术主要有助于晶体管开关速度的提升,并可减小栅极的漏电流。我们可以看到,Intel、AMD和台积电都在自己的制程工艺规划中加入了HKMG技术,说明这项技术得到了三巨头的普遍认可。图4是Intel 45nm制程NMOS管的HKMG结构实物图:因为篇幅有限再加上这两个技术点非常复杂,这里就不对应变硅和HKMG进行展开描述了。

图4

看到这里可能你会问,应变硅和HKMG技术不就可以让传统平面型晶体管一直延续下去了吗?非也,当制程下降到15nm以下后,传统平面型晶体管本身的技术壁垒将成为很难逾越的大山,除非在这段时间内又有新的“奇兵”技术出现。

传统平面型晶体管技术的瓶颈

尽管应变硅和HKMG技术曾经相当有效,而且在过去的一段时间里也起到了成功延续传统平面型晶体管寿命的重要作用,但以栅极宽度为代表的关键尺寸的不断减小所带来的负面效应已经越来越明显。

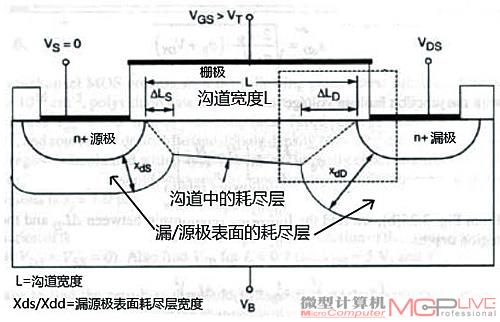

图5

首先,当栅极宽度减小到一定程度后,如图5所示,沟道的宽度(图中的L)也必然随之缩小,此时由于源、漏极区覆盖的耗尽层宽度(图中的XdS和XdD)在整个沟道中所占的比重增大,与沟道耗尽层重合程度也越来越大,这便会导致所谓的短沟道效应(SCE)。

什么是短沟道效应?

随着MOSFET沟道长度不断缩短,使得MOSFET出现了一系列在长沟道模型中得不到反映的现象,而这些原来可以忽略的效应变得愈发显著,甚至成为影响性能的主导因素,这种现象的统称即为短沟道效应。短沟道效应的坏处多多,首先是容易造成栅极门限电压Vt的上升,使管子的功耗增加;其次是可造成热载流子效应,影响器件寿命,另外还有可能造成管子无法关断,沟道中载流子迁移率下降等问题。

为了控制短沟道效应,人们不得不向沟道中掺杂磷、硼等杂质元素,这便导致用于控制管子开关的门限电压Vt的上升,同时还会降低沟道中空穴/电子流动的速度,造成管子速度的下降。而且用来向沟道中掺杂杂质的离子注入工艺也存在很难控制的问题,很容易造成管子门限电压过大等不良结果。其次,传统的SiGe PMOS应变硅技术也开始面临瓶颈,以Intel为例,截至目前为止,其应变硅技术在32nm制程节点中已经发展到了第4代。在Intel的第4代应变硅技术中,PMOS管漏源区内的eSiGe层掺杂的Ge元素比例也已经达到了40%的水平。很难再为沟道提供更高级别的应变。第三,栅极氧化物的厚度方面也将出现发展瓶颈问题。仍以Intel为例,其HKMG技术在32nm制程节点中已经发展到了第二代,其第二代HKMG技术中High-K绝缘层的厚度已经被减小到0.9nm的水平。

图6:图中下方Vt线为门限电压,上方两根线为管子饱和电流

和输入电流,制程越发展,工艺控制越困难。

IBM研发中心的高管Bruce Doris表示,栅极氧化物厚度减薄的速度已经很难再跟上栅极宽度缩小的步伐。而Intel公司负责制程技术的经理Mark Bohr也表示,Intel对现有结构的部分耗尽式平面型晶体管技术能否继续沿用到15nm制程节点感到“非常悲观”。

后,其它一些传统平面型晶体管所面临的问题也将越来越难解决。工作电压的不断升高,使芯片的功耗控制变得越来越困难;而且关键尺寸的缩小还会导致漏/源极电阻的不断增大。

突破传统平面型晶体管技术瓶颈的思路和方向

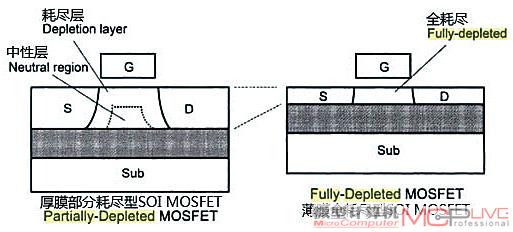

目前占主流地位的思路是放弃传统的平面型晶体管技术,想办法减小沟道区的厚度,消除沟道中耗尽层底部的中性层,让沟道中的耗尽层能够填满整个沟道区—这便是所谓的全耗尽型(Fully Depleted:FD)晶体管,而传统的平面型晶体管则属于部分耗尽型(Partialiy Depleted:PD)晶体管,两者之间的区别如图7所示:

图7:中性层消失后,沟道厚度降低,进一步抑制短沟道效应,

漏电流大大降低,同时还具有具有载流子迁移率增大,

电流驱动能力提高的优势,这都为进一步降低功耗打下了扎实的基础。

不过,要制造出全耗尽型晶体管,要求沟道所处的硅层厚度极薄,这样才有可能形成全耗尽式的结构。传统的制造工艺,特别是传统基于体硅的制造工艺很难造出符合要求的结构,即便对新兴的SOI工艺而言,沟道硅层的厚度也很难控制在较薄的水平。另外一种相对较新的思路则是在晶体管的平面型工艺技术不作太大变化的条件下,转而开发全新的晶体管材料。

不论是以上哪一种方式,都要求芯片制造商转而寻求其它的晶体管结构形式或制造材料,而这也意味着业界未来一段时间内的研发重心将从应变硅和HKMG等技术转向新型晶体管结构和新材料的研制方面。

Gartner的分析师Dean Freeman为此表示,目前半导体业界所面临的情况与1980年代非常类似,当时业界为了摆脱面临的发展瓶颈,开始逐步采用CMOS技术来制造内存和逻辑芯片,从而开创了半导体业界的新纪元。