SSD存储颗粒的现在与未来

2011年泰国的洪水把机械硬盘的价格推高了不少,却给SSD固态硬盘带来了一个新的发展契机,光刻技术与半导体技术的快速发展,也让SSD的成本方面逐渐降低。随着SSD在消费级市场的普及,用户也开始关心SSD存储颗粒的相关技术,读者也渴望了解主流SSD存储颗粒的相关知识。下面我们将向读者解析目前MLC NAND颗粒所采用的技术并深度剖析新的20nm存储颗粒的结构设计与生产工艺,后重点讲述下一代存储颗粒的原理与发展潜力。

ONFI与Toggle DDR接口标准争斗的白热化

相信大多数用户对SLC存储颗粒与MLC存储颗粒都有一定了解。MLC存储颗粒与SLC存储颗粒相比,以相同芯片面积上获得两倍存储容量的成本优势迅速赢取了消费级用户的青睐。SLC存储颗粒则退居追求高性能、稳定性的企业级市场。虽然所有厂商的MLC存储颗粒的原理基本相同,但因生产工艺与技术的不同,它们之间也存在着一定的差异。大的差异就是存储颗粒的接口标准,以英特尔、美光、海力士为主的ONFI(Open NAND Flash Interface)接口标准联盟;三星和东芝组成的Toggle DDR Model接口标准联盟。

ONFI阵营全家福。

现在ONFI接口标准已经发展到第三代,采用了DDR(Double Data Rate)信号技术与同步时钟控制,传输带宽达到了400MB/s。同时将SSD主控芯片中的ECC纠错功能集成到了存储颗粒内部,增加了主控芯片的效率。Toggle DDR接口标准也发展到了第二代,它与前者明显的差别在于采用了异步时钟控制。同步时钟控制是主控可以通过发送同步指令激活闪存上的同步时钟信号,使闪存与主控工作在同步模式,此时闪存的数据传输速率会大幅度提升。而Toggle DDR接口标准采用异步设计,异步时钟控制在主控发出指令以后,主控与闪存之间有一个时钟信号匹配的过程,然后再传输数据。

在理论上,异步时钟控制的时间延迟肯定是落后同步时钟控制。虽然如此,依靠三星和东芝在NAND方面的优势,Toggle DDR接口标准在各项技术产生上并没有落后老牌的ONFI接口标准,传输带宽也达到了400MB/s。加上现在主控的技术差异,两种接口标准的产品在实际测试体验差别不大,玩家们也不需要纠结选择何种存储颗粒,只要选择适合自己的就可以了。至于这两种接口的实际体验,可以参见《微型计算机》2012年6月下《“大”“快”人心,两款512GB固态硬盘深度体验》,两款产品分别是采用了英特尔同步颗粒的OCZ Vertex 4 512GB固态硬盘和采用东芝Toggle DDR异步闪存颗粒的浦科特PX-512M3 512GB固态硬盘。

单就原理而言,毫无疑问ONFI的优势还是要强于Toggle DDR,这两种接口标准的争斗我们可以看做是对新技术的探索,它所带来的技术革新的终受益者仍然是消费者。然而接口也只是SSD存储颗粒的一小部分,重要的仍然是存储单元,在小的芯片面积上集成多的存储容量才是解决SSD成本的根本原因。为了达到这一目的,厂商不断缩小MLC的制程工艺,英特尔目前已经将其工艺升级到了20nm。

英特尔20nm MLC的创新技术

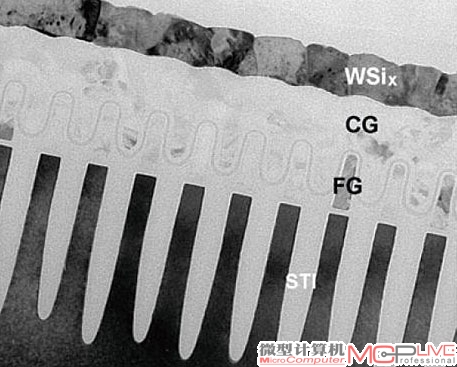

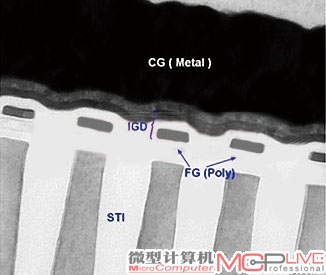

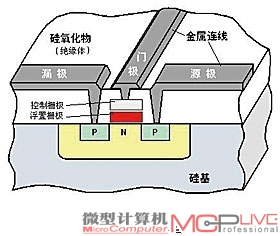

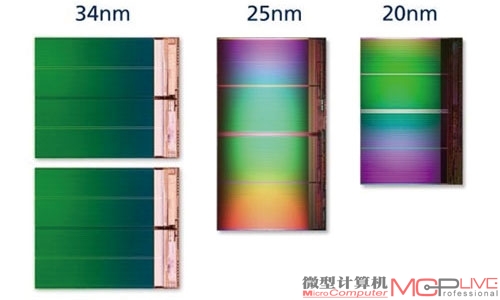

日前英特尔发布了20nm MLC存储颗粒样品,它的芯片面积也减少了不少,以64Gb颗粒为例,20nm工艺的芯片面积为117mm2,英特尔25nm工艺同容量的芯片面积为162mm2,新工艺节约了约30%的芯片面积。当然,这次升级并不只是在工艺上通过光刻来微小化存储单元,结构与材料上仍然发生一定的变化。25nm MLC存储单元的控制栅(Control Gate)和绝缘膜缠绕在浮栅(Floating Gate)上,控制栅与浮栅重合面积绝大多数在侧壁,耦合因子很大程度上也依赖于浮栅侧壁。随着存储单元之间的距离越来近,多晶硅材质的控制栅填入高深宽比的沟道已经非常困难了,单元与单元之间的干扰也越来越大。

为了解决上面的问题,英特尔20nm工艺采用了平面浮栅与控制栅结构,这种结构的浮栅与控制栅相比25m的栅结构减薄了许多。从25nm与20nm剖面图对比可以看出来,浮栅从陡峭的“高山”形状转变成了低矮的“长方形”的形状,控制栅形状也与浮栅类似了,这个结构实现了我们常见的理想化NAND结构。此时带来的问题就是控制栅与浮栅的重合面积越来越小,耦合因子也减少。但高介电常数的IGD栅间绝缘材料与金属控制栅(下简称金属栅)的引入很巧妙地解决这个问题,目前对高介电常数的IGD比常用的ONO(Oxide-Nitride-Oxide)栅间绝缘材料拥有更高的K值,增加了控制栅对浮栅的耦合率。金属控制栅相比多晶硅控制栅,电阻更低,导电能力更强,形成的电场均匀度也好。读者也许会问,如果金属栅有这么多的好处,为什么之前没有采用呢?这与半导体制造技术有关,硅是半导体物质(金属是导体),它一旦沾附金属离子(常见的Na+,Fe2+),则芯片就会失效,半导体制造中的前段和后端作业就是以金属工艺来作为分界线。而控制栅的工艺通常都是在前段作业完成,金属栅的应用必引来金属离子污染,为整个芯片生产线带来巨大的麻烦。

总体而言英特尔20nm存储颗粒给我们还是带来了较多的惊喜,更小的工艺带来更小的芯片面积,成本也自然会下降。截止发稿为止,有关20nm MLC的产品测试显示其性能较25nm产品有所下降。这也在意料之中,小的浮栅电荷存储减少,这将需要更灵敏的控制栅的来判断浮栅中是否存储有“数据”,同时在出错率方面也会大大增加,从而需要更强的纠错功能,这为读写速度带来了一定的拖累。

英特尔25nm与20nm剖面图以及理想的NAND结构。

SSD存储颗粒的未来

客观一点看,这次英特尔发布的20nm MLC存储颗粒只是减少了芯片面积,控制了芯片成本,而没有从根本上解决目前存储颗粒的读写速度与寿命;从原理层面来看,只要是基于EEPROM原理的NAND永远也逃脱不了低寿命、低稳定性的宿命。要么彻底改变存储单元的存储原理,要么新的材料出现,这样才能彻底拯救SSD,下面我们将来看几种可能取代目前NAND Flash的下一代SSD存储颗粒技术。

34nm、25nm、20nm相同容量存储颗粒面积对比。